- Digital Design An Embedded Systems Approach Using Verilog Solution Manual

- Digital Design An Embedded Systems Approach Using Verilog Pdf

- Digital Design An Embedded System Approach Using Verilog Ppt

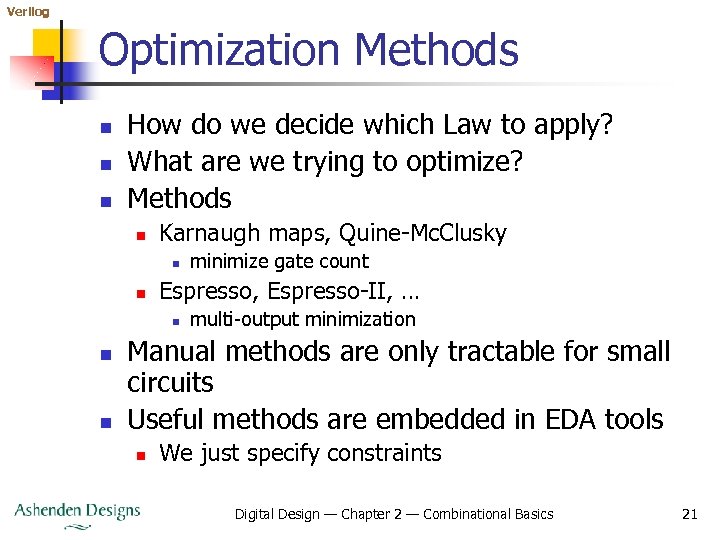

Ashenden P J digital Design an Embedded Systems Approach Using Verilog. Digital Design —Chapter 8 —I/O Interfacing 11. Example: Multiplexed Display. Four BCD inputs, 10MHz clock. Turn on decimal point of leftmost digit only. 50Hz scan cycle (200Hz scan clock) module displaymux ( output reg 3:0 anoden, output 7:0 segmentn, input 3:0 bcd0, bcd1, bcd2, bcd3, input clk, reset ); parameter clkfreq = 10000000; parameter scanclkfreq = 200; parameter clkdivisor =. Get this from a library! Digital design: an embedded systems approach using Verilog. Peter J Ashenden.

Teaching > Digital Logic1st year CTI-English, 2nd semester, year 2012/2013 - orar CTI_Eng_I. This page can also be found at: cs.upt.ro/~alext/dl

Resources

Source Code 1. Combinational 5-bit adder 3. LFSR Code Snippets input [3:0]x; output [6:0]y; reg [6:0]y; always @(*) begin case(x) 4'd0: y = 7'b1000000; 4'd1: y = 7'b1111001; 4'd2: y = 7'b0100100; 4'd3: y = 7'b0110000; 4'd4: y = 7'b0011001; 4'd5: y = 7'b0010010; 4'd6: y = 7'b0000010; 4'd7: y = 7'b1111000; 4'd8: y = 7'b0000000; 4'd9: y = 7'b0010000; default : y = 7'b1111111; endcase end endmodule output s, cout; assign s = x ^ y; output s, cout; /* assign s = x ^ y ^ cin; */ /* wire ws, wc1, wc2; hac h1(x, y, ws, wc1); */ // var 3 - 'software adept' assignment output [7:0]y; reg [7:0]y; always @(*) y = 8'b0; 3'd0: y = 8'b00000001; 3'd2: y = 8'b00000100; 3'd4: y = 8'b00010000; 3'd6: y = 8'b01000000; endcase parameter LIMIT = 8; input clk, rst; output overflow; reg [NBITS-1:0]count, count_next; always @(posedge clk or negedge rst) if(rst 0) else end always @(*) if(count LIMIT-1) else end assign overflow = (count 1) ? 1 : 0; endmodule

Logicly.zip |

Digital Design An Embedded Systems Approach Using Verilog Solution Manual

Digital Design An Embedded Systems Approach Using Verilog Pdf

Digital Design An Embedded System Approach Using Verilog Ppt

Teaching > Digital Logic1st year CTI-English, 2nd semester, year 2012/2013 - orar CTI_Eng_I. This page can also be found at: cs.upt.ro/~alext/dl

Resources

Source Code 1. Combinational 5-bit adder 3. LFSR Code Snippets input [3:0]x; output [6:0]y; reg [6:0]y; always @(*) begin case(x) 4'd0: y = 7'b1000000; 4'd1: y = 7'b1111001; 4'd2: y = 7'b0100100; 4'd3: y = 7'b0110000; 4'd4: y = 7'b0011001; 4'd5: y = 7'b0010010; 4'd6: y = 7'b0000010; 4'd7: y = 7'b1111000; 4'd8: y = 7'b0000000; 4'd9: y = 7'b0010000; default : y = 7'b1111111; endcase end endmodule output s, cout; assign s = x ^ y; output s, cout; /* assign s = x ^ y ^ cin; */ /* wire ws, wc1, wc2; hac h1(x, y, ws, wc1); */ // var 3 - 'software adept' assignment output [7:0]y; reg [7:0]y; always @(*) y = 8'b0; 3'd0: y = 8'b00000001; 3'd2: y = 8'b00000100; 3'd4: y = 8'b00010000; 3'd6: y = 8'b01000000; endcase parameter LIMIT = 8; input clk, rst; output overflow; reg [NBITS-1:0]count, count_next; always @(posedge clk or negedge rst) if(rst 0) else end always @(*) if(count LIMIT-1) else end assign overflow = (count 1) ? 1 : 0; endmodule

Logicly.zip |

Comments are closed.